International Journal of Digital Application & Contemporary Research Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

# Analysis of Total Harmonic Distortion and its Elimination by Multilevel Inverter

Nikhil Kumar Sharma

School of Electrical Sciences Indian Institute of Technology Bhubaneswar, Odisha, India- 751013 ns12@iitbbs.ac.in

#### Naveen Kumar Sahu

Electrical Engineering Departement Dr. C. V. Raman Institute of Science and Technology Bilaspur Chhattisgarh, India knaveen.cap1@gmail.com

Abstract-

As the conventional sources of energy are exhausting rapidly, the demand of renewable sources are increasing day by day. The major problems associated with these sources are voltage imbalance, harmonic content and switching losses due to the power electronics converter connected to these sources. The waveform of practical inverters are non-sinusoidal and contains certain harmonics, but for many applications such as high power application, various industries which involves use of machines and fans, sinusoidal supply with low distortion are required. This paper is aimed at investigating and analyzing effect of total harmonic distortion and its elimination using multilevel inverter. Simulation study of the output voltage waveform of 2-level, 3-level and 5-level three-phase diode clamped converters using sinusoidal pulse width modulation technique has been done and total harmonic distortion (THD) of all the levels are compared. The results obtained by varying the switching frequency of inverter is also compared. The record shows that as the number of level increases, total harmonic distortion decreases and quality of output voltage improves.

Index Terms/Keywords-

Multi-level Converters, H-bridge Multi-level Converter, Pulse Width Modulation, Two Level Converter, Three Level Converter, MATLAB, Total harmonic Distortion, Inverter.

F

# **1 INTRODUCTION**

HE converters that convert DC power to ac power are defined <sup>T</sup>as inverter. Moreover, AC power to DC is defined, as rectifier. The output voltage waveform of ideal inverters should he sinusoidal. However, the waveform of practical inverters is nonsinusoidal and contains certain harmonics. For low and medium power applications, square wave or quasi-square wave voltage may be acceptable. But for high power application, sinusoidal waveforms with low distortion are required. With the availability of high speed power semiconductor devices (PSD), the harmonic content of the output voltage can be minimized significantly by advanced pulse width modulated (PWM) switching techniques. Even though conventional PWM voltage source inverters (VSI) have advantages like minimum number of devices and simplicity in circuit topology and control, the major drawback is the presence of harmonics close to the switching frequency. In addition, they invariably require a bulky transformer for high voltage applications apart from the PSDs having very high ratings. The general structure of the multilevel converter is to synthesize a sinusoidal voltage from several levels of voltages, typically obtained from capacitor voltage sources. The so-called multilevel starts from three levels. A three-level converter, also known as a neutral-clamped converter, consists of two capacitor voltages in series and uses

the center tap as the neutral. Each phase leg of the three-level converter has two pairs of switching devices in series. The center of each device pair is clamped to the neutral through clamping diodes. The waveform obtained from a three-level converter is a quasi-square wave output. The diode-clamp method can be applied to higher-level converters. As the number of levels increases, the synthesized output waveform adds more steps, producing a staircase wave, which approaches the sinusoidal wave with minimum harmonic distortion. Ultimately, an infinite number of levels can obtain a zero harmonic distortion of the output wave. More levels also mean series devices can span higher voltages without device voltage sharing problems. Unfortunately, the number of the achievable voltage levels is quite limited not only due to voltage unbalance problems but also due to voltage clamping requirement, circuit layout, and packaging constraints. To date, hardware implementation has only been reported up to six levels for a back-to-back intertie application in which the voltage unbalance problem has been successfully overcome. The magnetic transformer coupled multipulse voltage source converter has been a well-known method and has been implemented in 18and 48pulse converters for battery energy storage and static condenser (STATCON) applications, respectively. Traditional magnetic coupled multipulse converters typically synthesize the staircase voltage wave by varying transformer turns ratio with

International Journal Of Digital Application & Contemporary Research

# International Journal of Digital Application & Contemporary Research Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

complicated zigzag connections. Problems of the magnetic transformer coupling method are bulky, heavy, and lossy. The capacitor voltage synthesis method is thus preferred to the magnetic coupling method. There are three reported capacitor voltage synthesis-based multilevel converters: diode-clamp, cascaded-inverters with separated dc sources. This thesis will describe operating principles of these capacitor voltage synthesis multilevel converters. Based on the features and constraints, the application areas of these multilevel converters will be addressed.[1] [3] [4].

## 2 MULTI-LEVEL CONVERTER

A dc voltage Vdc series connected capacitors constitute the energy tank for converter providing some nodes to which the multilevel converter can be connected .each capacitor has the same voltage Em which is given by

$$Em = \frac{Vdc}{m-1} \tag{1}$$

IJDACR

Where m denotes the number of levels[8]. The level is referred to as the number of nodes to which the inverter can be accessible. An m-level inverter needs (m-1) capacitors. There are several types of multilevel converters. The types of multilevel converters are: diode-clamped multilevel converters, flying-capacitor (also referred to as capacitorclamped) multilevel converters, and cascaded H-bridges multilevel converters At this point, it seems appropriate to discuss the difference between the terms multilevel converter and multilevel inverter. The term multilevel converter refers to the converter itself. Furthermore, the connotation of the term is that power can flow in one of two directions. Power can flow from the ac side to the dc side of the multilevel converter. This method of operation is called the rectification mode of operation. Power can also flow from the dc side to the ac side of the multilevel converter. This method of operation is called the inverting mode of operation. The term multilevel inverter refers to using a multilevel converter in the inverting mode of operation[9]. There are various kinds of multilevel inverter in which research has been done.

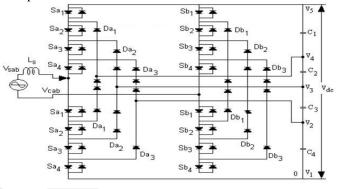

#### 2.0.1 Diode-clamped multilevel converters

An m-level diode-clamp converter typically consists of m - 1 capacitors on the dc bus and produces m levels of the phase voltage. It has the advantages when the number of levels are high enough, harmonic content will be sufficiently low to avoid the need for filters. Efficiency is high because all devices are switched at the fundamental frequency and reactive power flow can also be controlled. The control method is simple for a back-

to-back inter-tie [10] [17]. However it also has certain drawbacks such as excessive clamping diodes are required when the number of level is high [6] and it is difficult to do real power flow control for the individual converter [8][10].

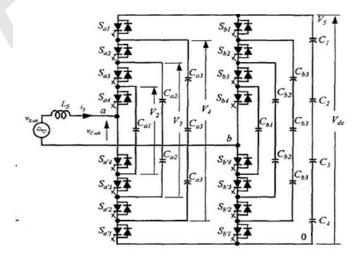

#### 2.0.2 Multilevel converter using flying capacitors

The fundamental building block of a single-phase fullbridge flying-capacitor based 5-level converter is shown in figure-2 [5]. Each phase-leg has an identical structure. Assuming that each capacitor has the same voltage rating, the series connection of capacitors is to indicate the

Fig. 1. A diode-clamp 5-level converter circuit

Fig. 2. Multilevel converter using flying capacitor circuit diagram

voltage level between the clamping points. Three innerloop balancing capacitors for phase leg a, Ca1, Ca2, and Ca3 are

International Journal Of Digital Application & Contemporary Research

International Journal of Digital Application & Contemporary Research Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

independent from those for phase leg b. All phase legs share the same dc link capacitors, C1-C4. The voltage level defined in the flying-capacitor converter is similar to that of the diode-clamp type converter[14]. The phase voltage of an m-level converter has m levels including the reference level, and the line voltage has (2m - 1) levels. Assuming that each capacitor has the same voltage rating as the switching device, the dc bus needs (m - 1) capacitors for an m-level converter. The voltage synthesis in a flyingcapacitor converter has more flexibility than a diodeclamp converter. Using Fig. 4 as the example, the voltage of the 5level phase-leg a output with respect to the negative dc rail, Vao, can be synthesized by the following switch combinations [27]. It has the advantage that large amount of storage capacitors provides extra ride through capabilities during power outage.It provides switch combination redundancy for balancing different voltage levels. When the number of levels is high enough, harmonic content will be low enough to avoid the need for filters[2][15]. However The inverter control will be very complicated, and the switching frequency and switching losses will be high for real power transmission[26].

IJDACR

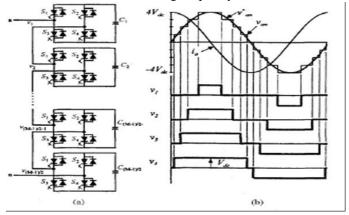

#### 2.0.3 H-Bridges Multi-level Converter

A relatively new converter structure, cascaded-inverters with separate dc sources (SDCs) is introduced here[24]. This new converter can avoid extra clamping diodes or voltage balancing capacitors. A relatively new converter structure, cascadedinverters with separate dc sources (SDCs) is introduced here. This new converter can avoid extra clamping diodes or voltage balancing capacitors. Each SDC is associated with a singlephase full-bridge inverter. The ac terminal voltages of different level inverters are connected in series. The phase output voltage is synthesized by the sum of four inverter outputs, i.e. Van=V1+V2+V3+V4 Each single-phase full bridge inverter can generate three level outputs, +vdc, O, and vdc. This is made possible by connecting the dc sources sequentially to the ac side via the four gate-turnoff devices. Each level of the full-bridge converter consists of four switches, S1,S2,S3, and S4.Using the top level as the example, turning on S1 and S4 yields V1=+Vdc Turing on S2 and S3 yields V1=-Vdc Turning off all switches yields V1 = 0. Similarly, the ac output voltage at each level can be obtained in the same manner. Minimum harmonic distortion can be obtained by controlling the conducting angles at different inverter levels[25]. With the phase current, ia leading or lagging the phase voltage Von by 90, the average charge to each dc capacitor is equal to zero over one line cycle, shown in Fig. 4.5 (b). Therefore, all SDC capacitor voltages can be balanced. To comply with the definition of the previously mentioned diodeclamp and flying-capacitor multilevel converters, the level in a cascaded-inverters based converter is defined by m = 2s + 1, where m is the output phase voltage level, and s is the number

of dc sources. For example, a multi -level cascaded inverters based converter will have four SDCs and four full bridges. For a three-phase system, the output voltage of the three cascaded inverters can be connected in either star or delta configuration [7]. It requires the least number of components among all multilevel converters to achieve the same number of voltage levels. Modularized circuit layout and packaging is possible because each level has the same structure, and there are no extra clamping diodes or voltage balancing capacitors.Soft-switching can be used in this structure to avoid bulky and lossy resistorcapacitor-diode snubbers[27]. However it needs separate dc sources for real power conversions, and thus its applications are somewhat limited.

# **3 RESULTS AND DISCUSSION**

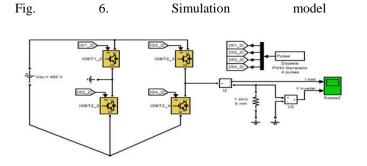

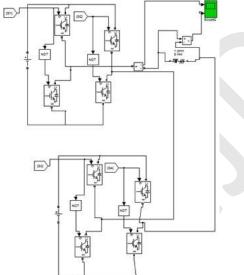

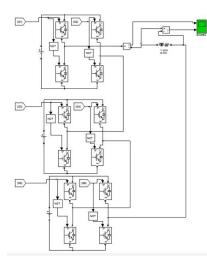

The study of the multilevel inverter with different levels has been carried out using SIMULINK software.Simulation model of the 3-phase voltage source 2 Level converter is shown in Fig. 5.Here 3 phase ac source is connected to 3 phase load through the phase cyclo-converter. Phase a phase b and phase c is connected to respective cyclo-converters via delta-delta connected. The three level contains four switches in each phase leg as compared to two switches in each leg in case of two-level Converter and five level contains 8 switching devices and 12 clamping diodes per phase leg. It produced 5-level output phase voltage.

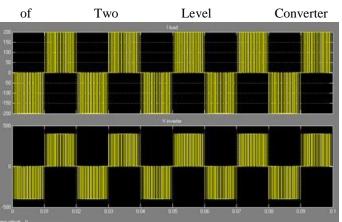

The output voltage waveform its frequency spectrum for two-level inverter at a switching frequency of 1 kHz are

Fig. 3. Cascaded converter based converter with separate dc sources. (a) Circuit diagram. (b) Waveform showing a 5 level converter phase voltage

IJDACR ISSN: 2319-4863

|                                                                                                                                                                                                                                       | 00            | IJDACR            |                | 1500                                                       | 25.94                                                                                                                                                                | 25.66                | 24.93       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|----------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|--|

|                                                                                                                                                                                                                                       | 0             | International Jou | rnal Of Digita | Applic <u>2500</u> & Cor                                   | ntempq <b>ıqıq</b> Resea                                                                                                                                             | rch 19.64            | 20.21       |  |

|                                                                                                                                                                                                                                       | International | Journal of D      | igital App     | lication <sup>5</sup> & Con                                | temporary Re                                                                                                                                                         | search <sup>83</sup> | 8.44        |  |

|                                                                                                                                                                                                                                       |               |                   |                | ume 4, <b>1</b> 990e 2, Se                                 |                                                                                                                                                                      | 5.37                 | 5.84        |  |

| shown in Figure 8.X axis shows the time in second while Y-axis shows voltage in volts.                                                                                                                                                |               |                   |                | Carrier<br>frequency(Hz)                                   | % THD Ph-A                                                                                                                                                           | % THD Ph-B           | % THD Ph-C⁴ |  |

|                                                                                                                                                                                                                                       |               |                   |                | Carrier<br>frequency(Hz)                                   | % THD Ph-A                                                                                                                                                           | % THD Ph-B           | % THD Ph-C  |  |

| Carrier<br>frequency(Hz)                                                                                                                                                                                                              | % THD Ph-A    | % THD Ph-B        | % THD Ph       |                                                            |                                                                                                                                                                      |                      |             |  |

| 1500                                                                                                                                                                                                                                  | 44.26         | 44.35             | 44.82          | various switch                                             | various switching frequencies are shown in table 2.<br>Table.2. Total Harmonic Distortion (THD) for 3-Level 3-<br>Phase Converter at Different Switching Frequencies |                      |             |  |

| 2500                                                                                                                                                                                                                                  | 40.48         | 40.73             | 40.63          | Table 2 Total                                              |                                                                                                                                                                      |                      |             |  |

| 3500                                                                                                                                                                                                                                  | 37.56         | 37.42             | 37.61          |                                                            |                                                                                                                                                                      |                      |             |  |

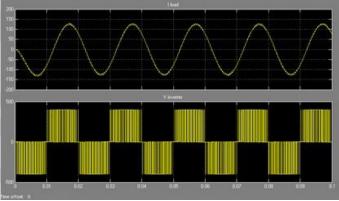

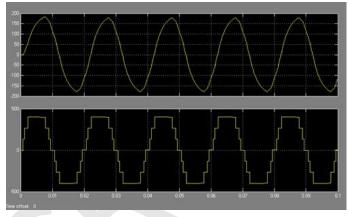

| 5000                                                                                                                                                                                                                                  | 31.83         | 31.54             | 31.67          | In Fig 10 output voltage its frequency spectrum of         |                                                                                                                                                                      |                      |             |  |

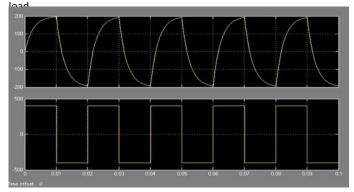

| Table.1. Total Harmonic Distortion (THD) for 2-Level 3-<br>Phase Converter at Different Switching Frequencies5level converter at switching frequency of 1 kHz are sho<br>Red yellow and blue colors indicates R,Y,B phases respective |               |                   |                |                                                            |                                                                                                                                                                      |                      |             |  |

| 1500                                                                                                                                                                                                                                  | 34.10         | 34.13             | 33.93          | and the corres                                             | ponding table is ta                                                                                                                                                  | able 3.              |             |  |

| 2500                                                                                                                                                                                                                                  | 22.05         | 22.39             | 22.52          | Table 2 Tatal                                              | Uarmonia Distant                                                                                                                                                     | on (TUD) for 5       | Laval 2     |  |

| 3500                                                                                                                                                                                                                                  | 14.68         | 14.93             | 14.89          |                                                            | Table.3 Total Harmonic Distortion (THD) for 5-Level 3-<br>Phase Converter at Different Switching Frequencies                                                         |                      |             |  |

| 5000                                                                                                                                                                                                                                  | 8.97          | 8.64              | 9.16           |                                                            | simulation results                                                                                                                                                   |                      |             |  |

| In figure 9 Output Voltage Waveform and Its Frequency $f$                                                                                                                                                                             |               |                   |                | ive-level three-phase converter, it has been shown that as |                                                                                                                                                                      |                      |             |  |

# IJDACR International Journal Of Digital Application & Contemporary Research 0

# **International Journal of Digital Application & Contemporary Research** Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

Fig. 4. Simulation model of Single Level Converter with R load

Fig. 5. Simulation model of Single Level Converter with R-L load

Fig. 8. Output voltage of 1-level Converter Frequency Spectrum for R

Fig. 9. Output voltage of 1-level Converter Frequency Spectrum for R-L

5

O IJDACR International Journal Of Digital Application & Contemporary Research

International Journal of Digital Application & Contemporary Research Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

Fig. 10. Output

voltage of 2-level inverter, and its Frequency Spectrum

Fig. 7. Simulation model of Five Level Converter

the number of levels has increased, system performance is improved in terms of total harmonic distortion and switching losses as well. The voltage impressed across the terminals of the switches is reduced further.

## 4 CONCLUSION

Simulation study and comparison of THD of the output voltage waveform of 2-level, 3-level and 5-level threephase diode clamped converters have been presented using SPWM technique. It has been noted that THD decreased with an increase in number of levels in output voltage. However, with decrease in carrier frequency, it was found that THD level has increased. Use of lower carrier frequency, however, allowed switching losses to be reduced proportionally.

Output voltage total harmonic distortion in 2-level, 3level and 5-level diode clamped Converter is compared at different switching frequencies. There is Variation of percentage THD for 2-level, 3-level and 5-level converter with carrier frequency. It is clear that as we go for higher number of levels and higher switching frequencies output power quality gets improved in terms of harmonic spectrum and overall losses of the system.

## **5 FUTURE SCOPE**

There are still some improvements which can be added to the system. First of all, it would be very interesting that the energy storage system such as battery or supercapacitor can be

integrated into the system. This will make the system more reliable. When there is no radiation at all, the system can still provide power from the energy storage system. Secondly, other micro-sources such as wind turbine can also be used as the

Fig. 11. Output voltage of 5-level inverter, and its Frequency Spectrum

micro-sources such as wind turbine can also be used as the separate DC sources for each module. However, the output of the wind turbine should be connected to the AC/DC converter to realize this.

## REFERENCES

- J. N. Chiasson, L. M. Tolbert, K. McKenzie and Z. Du "Harmonic Elimination in Multilevel Converters", 3rd ed. IASTED International Conference on Power and Energy Systems (PES 2003), February 24-26, 2003, Palm Springs, California, pp. 284-289.

- [2] J. S. Lai and F. Z. Peng, *Multilevel Converters A New Breed of Power Converters*, 3rd ed. IEEE Transactions on Industry Applications, vol. 32, no. 3, May 1996, pp. 509-517.

- [3] F. Z. Peng, J. W. McKeever and D. J. Adams, A Power Line Conditioner Using Cascade Multilevel Inverters for Distribution Systems, 3rd ed. IEEE Transactions on Industry Applications, vol. 34, no. 6, Nov. 1998, pp. 12931298.

- [4] L. M. Tolbert, F. Z. Peng and T. G. Habetler, A Multilevel Converter-Based Universal Power Conditioner, 3rd ed.

O IJDACR International Journal Of Digital Application & Contemporary Research

# International Journal of Digital Application & Contemporary Research Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

IEEE Transactions on Industry Applications, vol. 36, no. 2, Mar./Apr. 2000, pp. 596-603.

- [5] F.-S. Shyu and Y.-S. Lai, Virtual Stage Pulse-Width Modulation Technique for Multilevel Inverter/Converter, 3rd ed. IEEE Transactions on Power Electronics, vol. 17, pp. 332341, May 2002.

- [6] J. N. Chiasson, L. M. Tolbert, K. J. McKenzie, Z. Du, *Unified Approach to Solving the Harmonic Elimination Equations in Multilevel Converters*, 3rd ed. IEEE Transactions on Power Electronics, to appear in 2004.

- [7] L. M. Tolbert, F. Z. Peng, *Multilevel Converters as a Utility Interface for Renewable Energy Systems*, 3rd ed. IEEE Power Engineering Society Summer Meeting, July 15-20, 2000, Seattle, Washington, pp. 1271-1274.

- [8] F. Z. Peng and J. S. Lai, A static var generator using a staircase waveform multilevel voltage-source converter, 3rd ed. in Proc. PCIM/Power Quality, 1994, pp. 58-66.

- [9] N. S. Choi, G. C. Cho, and G. H. Cho, Modeling and analysis of a static var compensator using multilevel voltage source inverter, 3rd ed. in Conference Rec. IEEE/IAS Annu. Meeting, 1993, pp. 901-908.

- [10] C. Hochgraf, R. Lasseter, D. Divan and T. A. Lipo, Comparison of multilevel inverters for static var compensation, 3rd ed. in Conference Rec. IEEE/IAS Annu. Meeting, 1994,pp. 921-928.

- [11] M. Carpita and S. Teconi, A novel multilevel structure for voltage source inverter, 3rd ed. in Proc. EPE 1991, pp. 90-94.

- [12]F. Z. Peng and J. S. Lai, A multilevel voltage-source inverter with separate dc sources, 3rd ed. in Con Rec. IEEE/IAS Annu. Meeting, 1995, pp. 2541-2548.

- [13] F. Z. Peng and T. Fukao, A multilevel inverter for static var generator applications, 3rd ed. in IEE Jpn., Paper SPC-93-71, 1993.

- [14] F. Z. Peng, J. S. Lai, J. W. McKeever, and J. VanCOevering, A multilevel voltage-source converter system with balanced dc voltages, 3rd ed. in Conf Rec. IEEE Power Electron. Specialists Con, 1995, pp. 1144-1 150.

- [15] S. Lefebvre, A. M. Gole, J. Reeve, L. Pilotto, N. Martins, and S. Bhattacharya, *Working group on dynamic performance and modeling*" 3rd ed. 1993, pp. 595-601.

- [16] M. Bahman et al., Integration of small taps into existing HVDC links, 3rd ed. IEEE Paper 9SWM 273-3PWRD, 1995.multilevel PWM inverter, IEEE Trans. Ind. Applicat., vol. 19, no 6,pp. 1057-1069, Nov./Dec. 1983.

- [17] G.Bhuvaneswariand Nagaraju, Multi-Level Inveter-A comparative study 3rd ed. IETE Paper., vol. 51, no 2 ,pp. 141-153, march/april. 2005.

- [18] J. Rodriguez, J. S. Lai, and F. Z. Peng, *Multilevel Inverters:* a survey of topologies, controls, and applications. 3rd ed. IEEE Trans. Ind. Electronics, vol. 49, no. 4, pp. 724-738, August 2002.

- [19] A. Lesnicar, and R. Marquardt, An Innovative Modular Multilevel Converter Topology Suitable for a Wide Power Range, 3rd ed. IEEE PowerTech Conference, Bologna, Italy, June 23-26, 2003.

- [20] A. Lesnicar, and R. Marquardt, A new modular voltage source inverter topology, 3rd ed. EPE 2003, Toulouse, France, September 2-4, 2003.

- [21] A. Lesnicar, and R. Marquardt, New Concept for High Voltage - Modular Multilevel Converter, 3rd ed. IEEE PESC 2004, Aachen, Germany, June 2004.

- [22] M. Glinka and R. Marquardt, A New AC/AC Multilevel Converter Family, 3rd ed. IEEE Transactions on Industrial Electronics, vol. 52, no. 3, June 2005.

- [23] B.Gemmel, J. Dorn, D. Retzmann, and D. Soerangr, Prospects of multilevel VSC technologies for power transmission, 3rd ed. in Conf. Rec. IEEE-TDCE 2008, pp. 1-6.

- [24] M. Hagiwara, H. AkagiPWM Control and Experiment of Modular Multilevel Converters, 3rd ed. IEEE PESC 2008, Rhodes, Greece, June 2008.

- [25] A. Antonopoulos, L. Angquist, and H.-P. Nee, On dynamics and voltage control of the modular multilevel converter, 3rd ed. European Power Electronics Conference (EPE), Barcelona, Spain, September 8-10, 2009.

- [26] G.Bergna, M.Boyra, J.H.Vivas, *Evaluation and Proposal* of MMC-HVDC Control Strategies under Transient and Steady State Conditions 3rd ed.

- [27] P.Munch, S.Liu, M.Dommaschk Modeling and Current Control of Modular Multilevel Converters Considering Actuator and Sensor Delays 3rd ed.

- [28] M.Hagiwara, R.Maeda, H.Akagi, Control and Analysis of the Modular Multilevel Cascade Converter Based on DoubleStar Chopper-Cells (MMCC-DSCC) 3rd ed.

- [29] W.Li, L.A.Regoire, J.Blanger OPAL-RT Technologies (CAN), Control and Performance of a Modular Multilevel Converter System 3rd ed.

- [30] S. Rohner, J. Weber and S. Bernet Continuous Model of Modular Multilevel Converter with Experimental Verification, 3rd ed. Dresden University of Technology.

- [31] David Houcque, *Introduction To Matlab For Engineering Students*, 3rd ed., Northwestern University, 2005.

O IJDACR International Journal Of Digital Application & Contemporary Research

# International Journal of Digital Application & Contemporary Research Website: www.ijdacr.com (Volume 4, Issue 2, September 2015)

Nikhil Kumar Sharma was born in Bilaspur(Chhattisgarh),India on 10 April 1987.He received the B.Tech. degree from the National Institute of Technology Raipur, India in 2010,

Currently he is pursuing the M.Tech. degree in Indian Institute of Technology,

Bhubaneswar, India. His research interests are mainly in the applications of high voltage to air pollution control.

**Naveen Kumar Sahu** was born in Bilaspur (Chhattisgarh), India on 14 October 1989. He received the B.E. degree from the Government Engineering College Bilaspur in 2011, he has completed the M.Tech. degree in 2015 from Dr. CV Raman Institute of Technology And Science

, Bilaspur, India.